冯诺依曼瓶颈

天才冯·诺依曼

冯·诺依曼于 1903年12月28日出生在奥匈帝国的布达佩斯,1957年2月8日卒于美国,终年 53 岁。在他短暂的一生中,他取得了绝大的成就,远不止于世人熟知的“冯·诺依曼架构”。

约翰·冯·诺伊曼,出生于匈牙利的美国籍犹太人数学家家庭,现代电子计算机与博弈论的重要创始人,在泛函分析、遍历理论、几何学、拓扑学和数值分析等众多数学领域及计算机学、量子力学和经济学中都有重大贡献。

出列对计算机科学的贡献,他还有一个称号不为大众所熟知:“博弈论之父”。博弈论被认为是 20 世纪经济学领域最伟大的成果之一。(说到博弈论,我相信很多人第一个想到的肯定跟我一些样,那么就是“纳什均衡”)。

冯·诺依曼架构

冯·诺依曼由于在曼哈顿工程中需要进行大量的运算,从而使用了当时最先进的两台计算机 Mark I 和 ENIAC,在使用 Mark I 和 ENIAC 的过程中,他意识到了存储程序的重要性,从而提出了存储程序逻辑架构。

“冯·诺依曼架构”定义如下:

- 以运算单元为中心。

- 采用存储程序原理。

- 存储器是按地址访问、线性编址的空间。

- 控制流由指令流产生。

- 指令码由操作码和地址码组成。

- 数据以二进制编码。

优势

冯·诺依曼架构第一次将存储器和运算器分开,指令和数据均放置在存储器中,为计算机的通用性奠定了基础。虽然在规范中计算单元依然是核心,但冯·诺依曼架构事实上导致了以存储器为核心的现代计算机的诞生。

注:请各位在心里明确一件事情,“存储器指的是内存,即 RAM。”而磁盘在理论上属于输入输出设备。

该架构的另一项重要共现是使用二进制取代十进制,大幅降低了运算电路的复杂性。这为晶体管时代超大规模集成电路的诞生提供了最重要的基础,让我们实现了今天手腕上 Apple Watch 的运算性能能够远超早期大型计算机的壮举,这也是摩尔定律得以实现的基础。

瓶颈

冯·诺依曼架构为计算机大提速铺平了道路,却也埋下了一个隐患:在内存容量指数级增长以后,CPU 和内存之间的数据传输带宽称为了瓶颈。

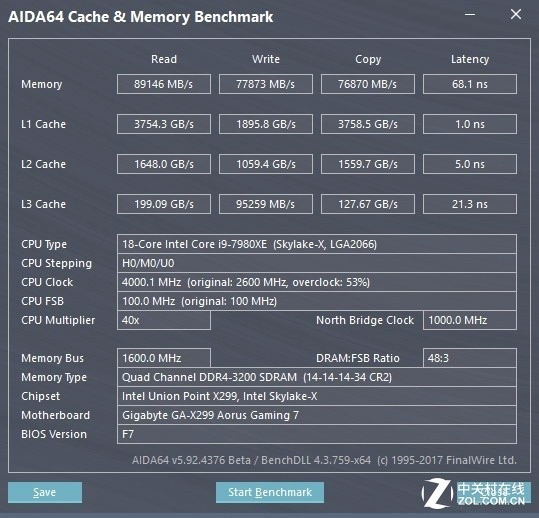

上图是 i9-7980XE 18 核 36 线程的民用最强 CPU,其配合超频过的 DDR4 3200MHz 内存,测试出的内存读取速度是 90GB/s。看起来是不是很快?看看图中的 L1 Cache,3.7TB/s。

我们再来算算时间。这颗 CPU 的最大睿频是 4.4GHz,就是说 CPU 执行一条指令需要的时间是 0.000000000227273 秒,即 0.22ns,而内存的延迟是 68.1ns。换句话说,只要去内存里读取一个字节,就需要 CPU 等待 300 个时钟周期,何其的浪费 CPU 时间啊。

CPU 的 L1/L2/L3 三级缓存是使用和 CPU 同样的 14 纳米工艺执照的硅半导体,每个 bit 都是用 6 个场效应管(即通俗讲的三极管)构成,成本高昂且非常占用 CPU 的核心面积,故不能做成很大的容量。

除此之外,三级缓存对计算机速度的提升来源于计算机内存的“局部性”,相关内容后续再展开讨论。

接下来

下一篇文章,我们将讨论分支预测、流水线与多个 CPU,看看那些上古大神为了提升性能都迸发出了什么奇思妙想,又都搞出了什么奇技淫巧。

Feedback

Was this page helpful?

Glad to hear it! Please tell us how we can improve.

Sorry to hear that. Please tell us how we can improve.